|

|

Скоро!Событий нет.

|

Главная » Новости » Новости перспективных технологий » Intel раскроет подробности своих 32-нм микросхем

Новости перспективных технологий31 октября 2008

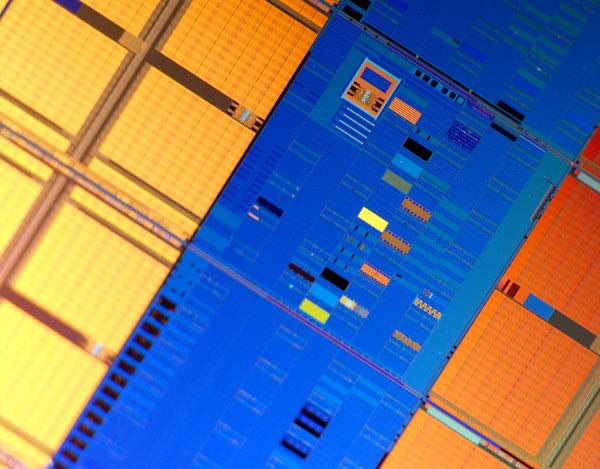

Intel раскроет подробности своих 32-нм микросхемФото с сайта www.3dnews.ru На грядущей конференции IEEE International Electron Devices Meeting (IEDM), по традиции, одним из главных докладчиков станет компания Intel, представители которой планируют раскрыть детали своего 32-нм технологического процесса для изготовления высокопроизводительных микропроцессоров. Согласно предварительной информации, разработчикам компании удалось создать тестовую интегральную микросхему статической SRAM-памяти емкостью 291 Мбит, причем площадь ячейки составляет 0,171 кв. мкм. При этом конструкция устройства составляет примерно 2 млрд транзисторов. Микросхема функционирует на частоте 3,8 ГГц при рабочем напряжении 1,1 Вольт.

Для изготовления интегральных микросхем по 32-нм технологическому процессу разработчики рассчитывают использовать иммерсионную литографию, причем соответствующее оборудование будет приобретаться у японской компании Nikon. Помимо этого используются такие технологии, как технология изготовления затворов с использованием металлических материалов и high-k-материалов, формирование многослойных диэлектрических структур и пр. Среди остальных докладов есть не менее интересные темы, например, технология изготовления CMOS-микросхем с интегрированными RF-элементами с применением транзисторов на основе фосфида индия, разработанная сотрудниками исследовательской лаборатории HRL Laboratories . Главное преимущество такого подхода – повышение скоростных показателей микросхем, по сравнению с традиционными кремниевыми устройствами, однако их существенным недостатком является сложность в изготовлении и высокая стоимость, по сравнению с кремниевыми аналогами. Интересным обещает быть и доклад сотрудников Университета Тохоку (Tohoku University), в котором будет затронута тема применения элементов на основе магнитного туннельного перехода для создания блоков хранения информации в микропроцессорах с 3D-структурой высокой плотности. Напоследок отметим, что ежегодная, 54-ая по счету, конференция IEDM пройдет с 15 по 17 декабря в Сан-Франциско. Информация с сайта www.3dnews.ru со ссылкой на eetimes.com. Автор оригинального текста: Александр Бакаткин. |

|

|

© “Элинформ” 2007-2026. Информационный портал для производителей электроники: монтаж печатных плат, бессвинцовые технологии, поверхностный монтаж, производство электроники, автоматизация производства  |