|

|

Скоро!Событий нет.

|

Главная » Новости » Новости перспективных технологий » Предложена новая методика получения 3D-транзисторов

Новости перспективных технологий21 июня 2012

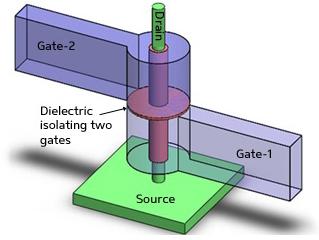

Предложена новая методика получения 3D-транзисторовИзображенние с сайта compulenta.ru

Идея заключается в том, чтобы размещать транзисторы один над другим на одном вертикальном нанопроводнике. Исследователи использовали так называемые опоясывающие затворы (wrap-around gates), имеющие цилиндрическую часть с проходящим в центре нанопроводником. Между затворами расположен изолирующий диэлектрический слой. Учёные уже продемонстрировали возможность создания простейшего логического элемента на основе всего одного нанопроводника и двух расположенных вертикально транзисторов. В предложенной схеме ток протекает в том случае, если напряжение на обоих затворах имеет высокое значение. При низком напряжении на любом из затворов ток течь перестаёт. За счёт вертикального размещения транзисторов занимаемая ими площадь сокращается вдвое. В перспективе предложенная методика может найти применение в электронных схемах с 3D-структурой. Информация с сайта compulenta.ru с ссылкой на phys.org. Автор оригинального текста: Владимир Парамонов. |

|

|

© “Элинформ” 2007-2026. Информационный портал для производителей электроники: монтаж печатных плат, бессвинцовые технологии, поверхностный монтаж, производство электроники, автоматизация производства  |

Сингапурские специалисты из Агентства по науке, технологиям и исследованиям (A*STAR) разработали новую методику 3D-компоновки, которая позволяет уменьшить площадь, занимаемую двумя транзисторами.

Сингапурские специалисты из Агентства по науке, технологиям и исследованиям (A*STAR) разработали новую методику 3D-компоновки, которая позволяет уменьшить площадь, занимаемую двумя транзисторами.